T-50-17

TC9125BP FM/AM (LW, MW, SW)/TV SYNTHESIZER PLL

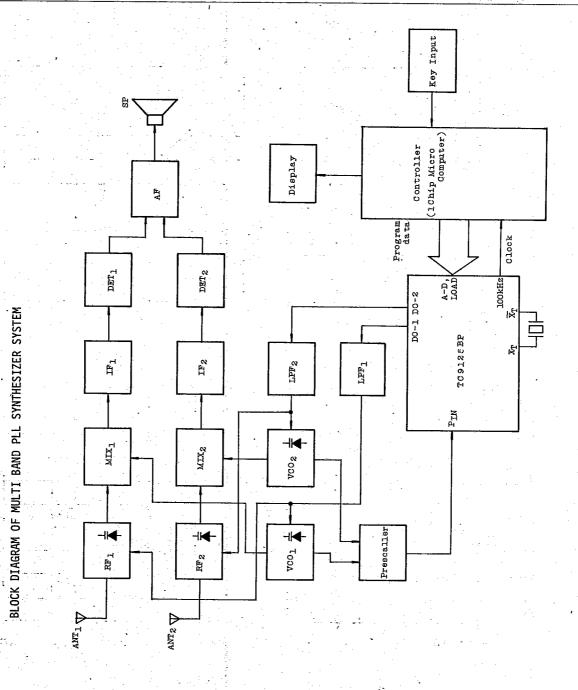

TC9125BP is CMOS LSI developed for the digital tuning system and has the following features.

- The system design with high flexibility allows the applications of frequency synthesizers covering all the frequency ranges of FM/LW/SW/MW and TV.

- High speed programmable counter has been realized by TOSHIBA's unique circuitry and process, and 1/8 frequency divider can be used as the prescaller for receiving FM signals obtaining high S/N ratio.

- When combined with prescaller TD6102P, IF

of FM receiving can be fine-tuned by 25kHz

shifting with the center frequency of 10.7MHz.

The channel step of 50 kHz for Europe can also be handled.

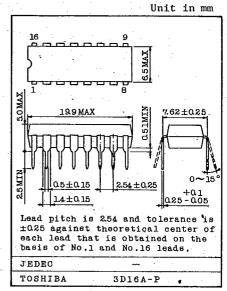

PIN CONNECTION

#### MAXIMUM RATINGS ( Ta=25°C )

|                                       | •                 |                             |      |

|---------------------------------------|-------------------|-----------------------------|------|

| CHARACTERISTIC                        | SYMBOL            | RATING                      | UNIT |

| Supply Voltage                        | $v_{\mathrm{DD}}$ | -0.3 ∿ 10.0                 | V    |

| Input Voltage                         | VIN               | $-0.3 \sim V_{DD} + 0.3$    | v    |

| Voltage Applied to<br>Output Terminal | Vour              | -0.3 ∿ V <sub>DD</sub> +0.3 | v    |

| Power Dissipation                     | $P_{\mathbf{D}}$  | 600                         | mW   |

| Operating Temperature                 | Topr              | -30 ∿ 70                    | °C   |

| Storage Temperature                   | Tstg              | -55 ∿ 125 ~                 | °C . |

- Having two phase comparator outputs, two kinds of low pass filters can be used without switching.

- TC9125BP has the input circuits most suitable for using a micro computer as its controller and the programming can be achieved through only five terminals, A through D and LOAD.

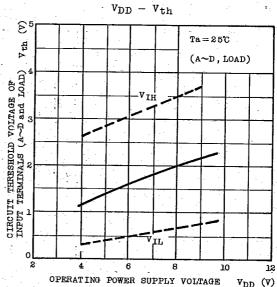

- The threshold voltage of the input terminals for program has been set low enough to eliminate limitation of power supply voltage when connected to a micro computer.

- Compact having 16 pin DIP arrangement.

#### FUNCTIONAL DESCRIPTION OF TERMINALS

| PIN<br>NO. | SYMBOL         | NAME OF TERMINAL                 | DESCRIPTION OF FUNCTION AND OPERATION | REMARKS                          |

|------------|----------------|----------------------------------|---------------------------------------|----------------------------------|

| 1          | GND            | Ground Terminal                  |                                       |                                  |

| 2<br>3     | X <sub>T</sub> | Crystal Oscil-<br>lator Terminal | Terminal to connect 9.0 MHz crystal   | Equipped with feedback resistor. |

| 4          | LOAD '         | Load Input                       | Input terminal for Read Com-          |                                  |

|            |                | Terminal                         | mand for the data on A through        |                                  |

|            |                |                                  | D. When this terminal is at           |                                  |

| <br>3.     | 2.4            |                                  | "1" level, the data is read in        | •, ••                            |

|            |                |                                  | and when it is at "0" level,          |                                  |

|            |                | i.e.                             | the previous data is retained         |                                  |

|            | Cyke.          |                                  | regardless of other inputs.           |                                  |

| 5          | A              | Program Data                     | Input terminals for the refer-        |                                  |

| 6          | В              | Input Terminals.                 | ence frequency selection data         |                                  |

| .7         | Ċ              |                                  | and the frequency division ratio      |                                  |

| 8          | D              |                                  | data for programmable counter,        |                                  |

| PIN<br>NO. | SYMBOL                                     | NAME OF TERMINAL                          | DESCRIPTION OF FUNCTION AND OPERATION                                                                                 | REMARKS                       |

|------------|--------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------|

| 9          | P <sub>IN</sub>                            | Programmable<br>Counter Input<br>Terminal | Input terminal of programmable counter.                                                                               | Equipped with input amplifier |

| 10<br>11   | P <sub>OUT</sub> -1<br>P <sub>OUT</sub> -2 | Programmable Counter Output Terminal      | Frequency division output terminal of programmable counter. Connected to pre-                                         |                               |

|            |                                            |                                           | scaller TD6102P for fine<br>adjustment of IF frequency of<br>FM and 50 kHz shifting in<br>Europe. Signals from Pout-1 |                               |

|            |                                            |                                           | and Pout-2 are output at the points of different phase.                                                               |                               |

| 12         | 100kHz                                     | 100kHz Clock Output<br>Terminal           | Output terminal of 100 kHz signal which can be utilized as the clock of micro computer.                               |                               |

| 13         | LD                                         | Lockout Detection<br>Terminal             | Holds "H" level during                                                                                                |                               |

| 14<br>15   | DO-1<br>DO-2                               | Phase Comparator<br>Output Terminals      | Connected to low pass filters.                                                                                        |                               |

| 16         | V <sub>DD</sub>                            | Supply Voltage<br>Terminal                | -                                                                                                                     | <u> </u>                      |

ELECTRICAL CHARACTERISTICS (Unless otherwise specified, Ta=25°C,  $V_{

m DD}$ =7.0V)

| CHARACTERISTIC                   | SYMBOL                   | TEST<br>CIRCUIT | TEST CONDITION                                                                                  | MIN.     | TYP. | MAX. | UNIT |

|----------------------------------|--------------------------|-----------------|-------------------------------------------------------------------------------------------------|----------|------|------|------|

| * Operating Supply               | V <sub>DD</sub> (1)      |                 | P <sub>IN</sub> =11MHz, V <sub>IN</sub> =1.7V <sub>P</sub> -p                                   | 5.5      | -    | 9.0  | V    |

| Voltage Range                    | V <sub>DD</sub> (2)      |                 | P <sub>IN</sub> =16MHz, V <sub>IN</sub> =1.7Vp-p                                                | 7.0      | -    | 9.0  | V    |

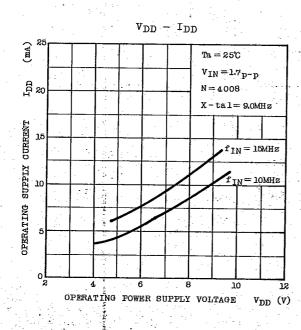

| * Operating Supply Current       | I <sub>DD</sub> (1)      |                 | $V_{ m DD}$ =6.0V, $P_{ m IN}$ =10MHz<br>9.0MHzX-Tal is connected<br>to XT - $\overline{ m XT}$ | -        | 6.0  | 12.0 | mА   |

|                                  | I <sub>DD</sub> (2)      |                 | $V_{DD}=8.0V$ , $P_{IN}=15MHz$<br>9.0MHzX-tal is connected to $X_T-\overline{X_T}$              | _        | 11.0 | 18.0 | mA   |

| (Programmable Counter)           | (PIN)                    |                 |                                                                                                 |          |      |      |      |

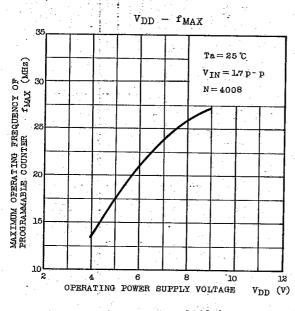

| * Maximum Operating              | f <sub>MAX</sub> (1)     |                 | V <sub>DD</sub> =5.5V, V <sub>IN</sub> =1.7V <sub>P</sub> -p                                    | 11       | -    | 1.   | MHz  |

| Frequency                        | f <sub>MAX</sub> (2)     |                 | V <sub>DD</sub> =7.0V, V <sub>IN</sub> =1.7V <sub>P</sub> -p                                    | 16       | -    | ī    | MHz  |

| * Minimum Operating<br>Frequency | f <sub>MIN</sub>         |                 | V <sub>DD</sub> =5.5 ∿ 9.0V,<br>V <sub>IN</sub> =1.7Vp-p                                        | <u>.</u> | -    | 200  | kHz  |

| * Operating Input<br>Amplitude   | $v_{IN}$                 |                 | V <sub>DD</sub> =7.0V, P <sub>IN</sub> =16MHz                                                   | 1.7      | -    | 6.0  | Vp-p |

| (Reference Frequency)            | $(X_T - \overline{X}_T)$ | ·               | V <sub>DD</sub> =5.5V                                                                           |          |      | -    |      |

| * Maximum Operating<br>Frequency | f <sub>MAX</sub>         |                 | 9.0MHzX-Tal is connected to $X_T$ - $\overline{X}_T$                                            | 9        | -    | · +- | MHz  |

| (Program Input)<br>Terminal      | (LOAD,)                  |                 | **************************************                                                          |          |      | ,    |      |

| * Threshold Voltage              | Vth (1)                  |                 | V <sub>DD</sub> =6.0V                                                                           | 0.5      | -    | 3.1  | v    |

| Range                            | Vth (2)                  | ,               | V <sub>DD</sub> =8.0V                                                                           | 0.7      | -    | 3.5  | v    |

T-50-17

| CHARACTERI                | STIC              | SYMBOL                           | TEST<br>CIRCUIT | TEST CONDITION                         | MIN. | TYP. | MAX. | UNIT |

|---------------------------|-------------------|----------------------------------|-----------------|----------------------------------------|------|------|------|------|

| Input<br>Leakage          | "H" Level         | I <sub>IH</sub>                  |                 | V <sub>IH</sub> =9.0V                  |      | _    | 10   | μА   |

| Current                   | "L" Level         | IIL                              |                 | V <sub>IL</sub> =0V                    | -    | _    | -10  | μΑ   |

| ("H" Level Out            | <sup>tput</sup> ) | (I <sub>OH</sub> )               |                 |                                        |      |      |      |      |

| P <sub>OUT</sub> -1,2 Out | put               | IOHPOUT                          | •               | •                                      |      |      |      |      |

| 100kHz Out                | put               | I <sub>OH</sub> 100kHz           |                 | v <sub>OH</sub> =6.0v                  | -0.3 | -    | -    | mA   |

| LD Out                    | put               | I <sub>OH</sub> DO               |                 |                                        |      |      |      |      |

| DO - 1,2 Out              | put               | IOH DO                           |                 |                                        |      |      |      |      |

| ("L" Level Out            | tput)             | (I <sub>OL</sub> )               |                 |                                        |      |      |      |      |

| POUT-1,2 Out              | put               | I <sub>OL</sub> P <sub>OUT</sub> |                 |                                        |      |      |      |      |

| 100kHz Out                | put               | I <sub>OL</sub> 100kHz           |                 |                                        |      |      |      |      |

| LD Out                    | put               | IOL LD                           |                 | V <sub>OL</sub> =1.0V                  | 0.3  | -    | -    | mA.  |

| DO - 1,2 Out              | put               | IOL DO                           |                 |                                        |      |      |      |      |

| (DO Tri-state<br>Current  | Leakage)          |                                  |                 | ************************************** |      |      | :    |      |

| Leakage                   | "H" Level         | ITLHDO                           |                 | v <sub>DD</sub> =9.0v                  | -    | _    | 100  | nA   |

| Current                   | "L" Level         | ITLLDO                           |                 |                                        | _    | _    | -100 | nA   |

| Feedback resis            |                   | Rf                               | 557             | -                                      | 100  | 250  | 500  | kΩ   |

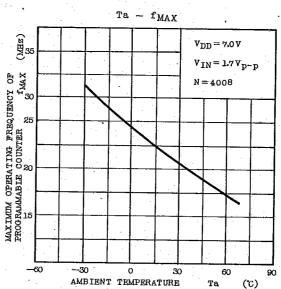

Note: Temperature range of Ta=-30  $\sim$  70°C for all the items marked with \*.

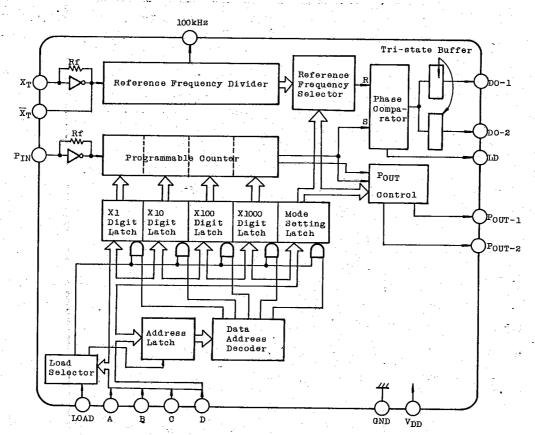

**BLOCK DIAGRAM**

#### FUNCTIONAL DESCRIPTION OF EACH BLOCK

- 1. REFERENCE FREQUENCY DIVIDER

- The reference frequency divider consists of the crystal oscillator amplifier having externally connected 9.0 MHz crystal and the frequency divider which divides the oscillator output to generate the reference frequency.

\*TOSHIBA

T-50-17

TC9125BP is provided with the following six kinds of reference frequencies to enable to be applicable for FM/LW/MW/SW and TV.

| Table | 1 | • |

|-------|---|---|

|       |   |   |

DE

| Mode                      | LW   | SW   | AM2  | AM <sub>1</sub> | FM   | TV     |

|---------------------------|------|------|------|-----------------|------|--------|

| Frequency Division Factor | 9000 | 1800 | 1000 | 900             | 720  | 576    |

| Reference Frequency [kHz] | 1.0  | 5.0  | 9.0  | 10.0            | 12.5 | 15.625 |

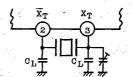

- 2) One of reference frequencies is selected by the signal from the data latch for mode setting and fed to the reference input of the phase comparator.

- 3) The amplifier for crystal oscillator is equipped with the bias resistor making the external circuit very simple as shown in Fig. 1.

Crystal: 9.00MHz HC-18/u Type

CL : 33pF

Fig. 1

4) The output terminal for 100 kHz is separately provided in the reference frequency divider and this signal can be utilized as the clock of micro processor which is the controller of TC9125BP.

$100~\mathrm{kHz}$  signal usually appears at  $100~\mathrm{kHz}$  output but  $125~\mathrm{kHz}$  signal will be seen only during TV mode.

E DE

#### 2. PROGRAMMABLE COUNTER

- The programmable counter is the frequency divider which can control

the frequency division factor according to the program data given

externally and has the arrangement of four BCD digits (16 bits).

- Since the programmable counter of TC9125BP is especially high speed,

1/8 frequency divider can be used for the prescaller of FM receiving.

- 3) The frequency division range of TC9125BP is

Frequency Division Factor N =  $80 \sim 9999$

and the frequency division factor is same as the program data given by the controller.

Therefore, there is the difference which corresponds to the intermediate frequency in PLL of receiver between the receiving frequency and the oscillating frequency of VCO (local oscillator) to normally control the local oscillator, and the frequency division offset which corresponds to IF frequency is controlled by the controller side for TC9125BP.

- 4) The frequency division output of the programmable counter is fed to the signal input (S) of the phase comparator and compared with the output frequency of the reference frequency divider.

- 5) And this frequency divider output is fed to the P<sub>OUT</sub> control circuit where the signal is output to programmable counter output terminals P<sub>OUT</sub>-1 and P<sub>OUT</sub>-2. By utilizing these two terminals, dedicated prescaller TD6102P is controlled to provide the capabilities of IF fine tuning for FM receiving and 50 kHz channel step for European areas.

Detail of this operation is described later.

T-50-17

6) As frequency input terminal  $P_{\rm IN}$  of the programmable counter is equipped with a self biased amplifier, the input signal is given through capacitor coupling and small amplitude is enough for proper operation.

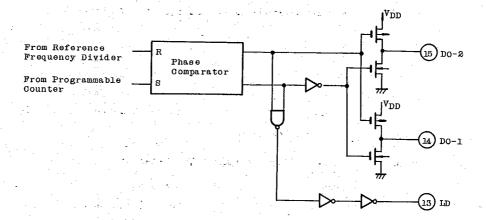

#### 3. PHASE COMPARATOR

The phase comparator is the circuit block which compares the phases of reference frequency divider output and programmable counter output and controls VCO through the low pass filter to coincide the frequencies and the phases of these two signals.

- 1) Outputs of DO-1 and DO-2 Terminals (CMOS Tri-state Outputs)

- a) When the phase of programmable counter frequency divider output lags behind that of reference frequency, DO-1 and DO-2 outputs become "L" level by turning on N-channel FET's for the period equivalent to the phase difference.

- b) On the contrary, when it leads, DO-1 and DO-2 outputs become "H" level by turning on P-channel FET's for the period equivalent to the phase difference.

- c) For the period when none of the aboves are seen, DO-1 and DO-2 outputs have high impedance by turning off both N-channel and P-channel FET's.

- 2) As TC9125BP is equipped with two tri-state outputs DO-1 and DO-2, two sets of low pass filters can be used without switching and the constants of low pass filters can be set to the optimum values for the multi-band applications.

- 3) Output of LD Terminal

- a) LD terminal is provided to detect the unlock operational state of PLL loop.

b) LD output becomes "H" level for the phase error time period during lock out. (Refer to Fig. 2)

FIG. 2 CIRCUIT OF PHASE COMPARATOR BLOCK

#### 4. POUT CONTROL CIRCUIT

- 1) TC9125BP is equipped two programmable counter outputs  $P_{\rm OUT}$ -1 and  $P_{\rm OUT}$ -2 and the output conditions of these two are controlled in the  $P_{\rm OUT}$  control circuit by the signal from the reference frequency data latches.

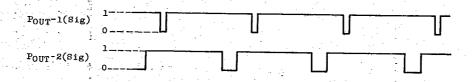

- 2) The signals of  $P_{OUT}-1$  and  $P_{OUT}-2$  are output with different phases each other as shown in Fig. 3.

FIG. 3 OUTPUTS OF POUT-1 AND POUT-2

T-50-17

#### 5. DATA LATCHES

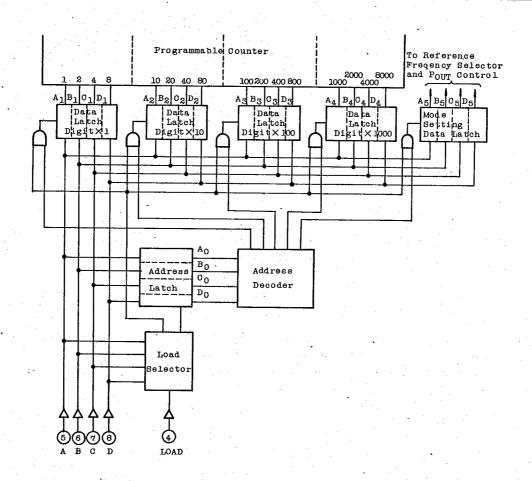

- 1) Because the mode setting data for reference frequency selection and POUT control and the data to set the programmable counter frequency division factor are input from four input terminals A through D in 4 bit serial for TC9125BP, 4bits × 5 latch circuits are provided in LSI where the program data is stored being converted to parallel.

- 2) As the circuit threshold voltage of program input terminals A through D and LOAD has been set low eliminating limitation of power supply voltage for connecting micro computer as its controller, it can be directly connected without any interface circuits.

- 3) The configuration of data latches is as shown in Fig. 4.

When the binary input signal from A through D is from 11 (hexadecimal B) to 15 (hexadecimal F), LOAD signal is sent to the address latches through the load selection circuit and the data is stored in the address latches. Then a data latch corresponding to the input data is designated by the address decoder.

And when the input from A through D is 0  $\sim$  9, LOAD signal is sent to the data latches and the input data is stored in the data latchs designated by the address decoder.

Fig. 4 CONFIGURATION OF DATA LATCH

#### RECEIVING BAND OF TC9125BP

TC9125BP has the system structure with high flexibility enabling to handle all the bands of FM/LW/MW/SW and TV.

T-50-17

In FM band, receiving with 50 kHz channel space has become possible for European areas by means of coupled control with dedicated prescaller TD6102P in addition to domestic FM and international FM.

1. The following six kinds of reference frequencies are provided as shown in Table 1.

1 kHz, 5 kHz, 9 kHz, 10kHz, 12.5 kHz, 15.625 kHz

The programmable counter does not have the frequency division factor offset. Table 1 shows each receiving band corresponding to reference frequency, but what reference frequency is used for what band can be freely selected according to the design specification of micro computer which is to be the controller. In this case, the frequency division factor offset corresponding to IF frequency is set accordingly by the controller side.

2. If reference frequency of FM band is set to 12.5 kHz, 1/8 prescaller can be used to realize high S/N ratio. The prescaller for TV band is 1/64.

#### PROGRAMMING OF TC9125BP

TC9125BP has the optimum input circuits for using a micro computer as its controller and the programming can be achieved through five terminals, A through D and LOAD.

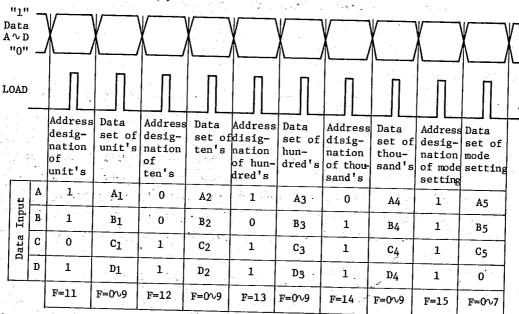

As the program data which instruct the operations of TC9125BP, there are the mode setting data to select the reference frequency and to control the  $P_{\rm OUT}$  output and the data to set the programmable counter frequency division factor. These data are input in 4 bit serial from four terminals A through D and converted to parallel in LSI being set in 4 bits  $\times$  5 latches.

2. In order to determine in what latch the data is set, the data which designates the address of latch is input first, then the data to be set in the latch is input. Whether the input data is frequency division factor data, mode setting data or address data is automatically selected in LSI according to the contents of A through D.

The address of each latch is as shown in Table 2.

Table 2 Latch Address

|         |           | <del></del> | r           |              | 1.0             |

|---------|-----------|-------------|-------------|--------------|-----------------|

| Latch   | Digit × 1 | Digit × 10  | Digit × 100 | Digit × 1000 | Mode<br>Setting |

| Address | F = 11    | F = 12      | F = 13      | F = 14       | F = 15          |

Where,  $F = 1 \cdot A + 2 \cdot B + 4 \cdot C + 8 \cdot D$ , A, B, C, D = "1" or "0"

T-50-17

Data input is performed in 4 bit binary.

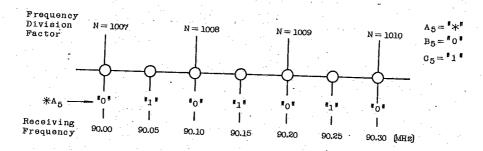

4. The mode of reference frequency and  $P_{OUT}$  terminals varies according to mode setting data A5, B5, C5 (D5 = "0") as shown in Table 3.

Table :

| REFERENC | REFERENCE FREQUENCY DATA REFERENCE |      |                    |                     |                     |

|----------|------------------------------------|------|--------------------|---------------------|---------------------|

| A5       | В5                                 | C5 - | FREQUENCY<br>[kHz] | P <sub>OUT</sub> -1 | P <sub>OUT</sub> -2 |

| 0        | 0                                  | 0    | 1                  | Sig.                | 1                   |

| .1       | 0                                  | 0    | 5                  | Sig.                | 1                   |

| 0        | 1                                  | 0    | . 9                | Sig.                | 1                   |

| 1        | 1                                  | 0    | 10                 | Sig.                | 1                   |

| 0        | 0                                  | 1    | 12.5               | 1                   | Sig'.               |

| 1        | 0                                  | 1    | 12.5               | Sig.                | Sig'.               |

| 1        | 1                                  | 1    | 15.625             | Sig.                | Sig'.               |

<sup>&</sup>quot;1" indicates that "H" level is retained.

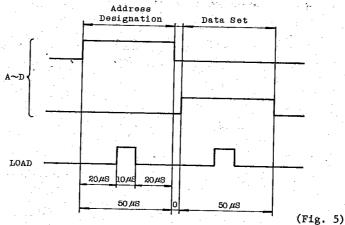

5. Load signal input is the input to instruct to read in the data given on terminals A through D. While this input is "1", the data on A through D are read into the internal latches and when it is "0", the previously read data are retained regardless of A through D.

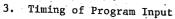

In order to prevent erroneous data read operation at the time of changing data on A through D, it is desirable to give the signal described in 3 Timing of Program Input.

<sup>&</sup>quot;Sig." and "Sig'." are frequency divided outputs of the programmable coutner. (Refer to Fig. 3.)

6. Minimum Pulse Width of Input Data

- 7. It is effective for improving S/N ratio of the radio set to transfer the input data once immediately after selection of station and to inhibit the transfer afterward keeping all of terminals A through D and LOAD at "L" level.

- Example of Program

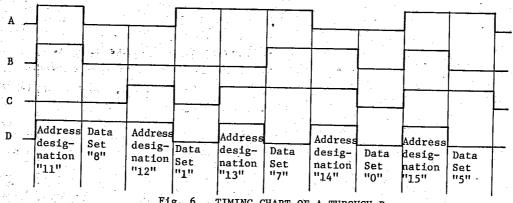

As an example of program for TC9125BP, the timing chart of A through Dwhen receiving 82.5 MHz of Japan FM band (reference frequency : 12.5kHz) is shown in Fig. 6.

Fig. 6 TIMING CHART OF A THROUGH D

T-50-17

The frequency division factor of programmable counter is 825 - 107 = 718:

\* There is FM/AM synthesizer controller TC9128P/29P using one chip micro computer TCP4620P as the controller of TC9125BP.

#### FINE ADJUSTMENT OF INTERMEDIATE FREQUENCY FOR FM RECEIVING

Since IF frequency in FM band of TC9125BP can be freely selected from seven kinds of frequencies,  $\pm 25$ ,  $\pm 50$  and  $\pm 75$  kHz around standard 10.7 MHz. the variations of IF filters used can be compensated realizing ideal receiving condition.

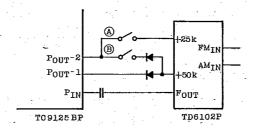

This operation is achieved by the program data control by the controller and the combination of TC9125BP and prescaller TD6102P. The operation is described in detail below.

- 1. The basic principles of this operation are as follows.

- 12.5 kHz is selected as the reference frequency of TC9125 BP and TD6102P is used as the prescaller.

- 2) It is required for the controller to have the function which arbitrarily forces the frequency division data sent to TC9125BP to be -1.

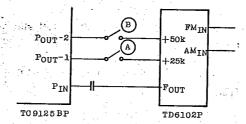

- 3) When one of POUT-1 and POUT-2 of TC9125BP is connected to +25 kHz terminal of TD6102P, the frequency of local oscillator is shifted by +25 kHz.

- 4) Similarly, when one of POUT is connected to +50 kHz terminal, it is shifted by +50 kHz.

- 5) When both of +25 kHz and +50 kHz terminals are connected to one of  $P_{\rm OUT}$ , it is shifted by +75 kHz.

- 6) Since programmable counter frequency divider outputs  $P_{OUT}-1$  and  $P_{OUT}-2$  are output with different phases, if both of these are connected to +25 kHz terminal, it is shifted by +50 kHz.

- 7) Similarly, if both of  $P_{\rm OUT}$  are connected to +50 kHz terminal, it is shifted by +100 kHz.

- 8) If both of  $P_{OUT}-1$  and  $P_{OUT}-2$  are connected to both of +25 kHz an +50 kHz, it is shifted by +150 kHz.

However, the above descriptions are applicable when the frequency division outputs exist on both terminals of  $P_{\rm OUT}-1$  and  $P_{\rm OUT}-2$ .

- 9) When the frequency division data is forced to be -1 by the controller, the local oscillator is shifted by -100 kHz.

- 10) In the case of domestic FM, when the local oscillator frequency is shifted by +4f, IF frequency will be 10.7 MHz 4f and when shifted by 4f, IF will be 10.7 MHz + 4f.

- 11) In the case of international FM, on the contrary, when shifted by  $+ \Delta f$ , IF will be 10.7 MHz  $+ \Delta f$  and when shifted by  $\Delta f$ , IF will be 10.7 MHz  $\Delta f$ .

- 2. An example of connecting TC9125BP and TD6102P is shown.

The mode setting data sent to TC9125BP are  $A_5$  = "1",  $B_6$  = "0" and  $C_5$  = "1" (F = 5).

Fig. 7

T-50-17

3. Connections for performing seven kinds of IF fine adjustments in Fig. 7 are as shown in the table below.

Table 4

| DESIRED I | F FREQUENCY |   | DOMESTIC FM |                                     |   | NTERNA | TIONAL FM                           |

|-----------|-------------|---|-------------|-------------------------------------|---|--------|-------------------------------------|

| IF [MHz]  | ⊿ IF [kHz]  | A | B           | FREQUENCY<br>DIVISION<br>FACTOR - 1 | A | B      | FREQUENCY<br>DIVISION<br>FACTOR - 1 |

| 10,775    | +75         | 0 |             | 0                                   | 0 | 0      |                                     |

| 10.750    | +50         |   | 0           | 0                                   |   | 0      |                                     |

| 10.725    | +25         | 0 | 0           | 0                                   | Ö |        |                                     |

| 10.700    | 0           |   |             |                                     |   |        |                                     |

| 10.675    | <b>-</b> 2Š | 0 |             |                                     | 0 | 0      | 0                                   |

| 10.650    | -50         |   | 0           |                                     |   | 0      | 0                                   |

| 10.625    | <b>-</b> 75 | 0 | 0           |                                     | 0 | - "    | 0                                   |

- (Notes) 1. 0 in the columns of (A) and (B) indicates that switch (A) and/or switch (B) should be turned on.

- 2. 0 in the column of Frequency division factor-1 indicates that the frequency division data sent to TC9125BP should be -1 shifted by the controller.

- 4. IF fine adjustment can be achieved with 50 kHz Channel Step in FM Band in Europe, but it is explained in the item of 50 kHz Channel Step.

5. IF Fine Adjustment without -1 Shift Function in Controller

As described above, it is required to have the function which performs -1 shift of frequency division data in the controller for seven kinds of IF fine adjustments, but it is also possible to achieve IF fine adjustment without this function. In this case, however, there are five kinds of IF fine adjustments.

The controller should be so designed that the frequency division data to TC9125BP in FM band has been -1 shifted from the actual frequency division data in advance.

Namely, the frequency division data in FM is always programmed in TC9125BP with the value shifted by -1.

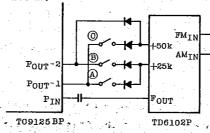

- 2) The mode setting data of TC9125BP shall be A5 = "1", B5 = "0" and C5 = "1".

- 3) Connection of TC9125BP and TD6102P is shown in Fig.8.

Fig.

4) Table 5 shows the connections for performing IF fine adjustment without the controller having the function of shifting the frequency division data by -1.

T-50-17

Table 5

| DESIRED I | F FREQUENCY | DOM | ESTIC | FM | INTERNATIONAL F |   |   |

|-----------|-------------|-----|-------|----|-----------------|---|---|

| IF [kHz]  | ⊿ IF [kHz]  | A   | B     | ©  | A               | В | © |

| 10.750    | +50         |     |       |    | 0               | 0 | 0 |

| 10,725    | +25         |     | 0     |    |                 | 0 | 0 |

| 10.700    | 0 *         |     |       | 0  |                 |   | 0 |

| 10.675    | -25         |     | 0     | 0  |                 | 0 |   |

| 10.650    | -50         | 0   | 0     | 0  |                 |   |   |

Note: 0 indicates that the respective switch should be turned on.

#### APPLICATION OF 50 KHz Channel Step in FM Band

The channel space of domestic FM and international FM is 100 kHz, however, there are some areas in Europe where the spacing is only 50 kHz. TC9125BP can be used in the radio sets for these areas. And IF fine adjustment with 50 kHz step can be achieved.

- 1. Basic operation of TC9125BP with 50kHz channel step is as follows.

- 1) As shown in Table 3, the output of  $P_{OUT}$ -1 terminal of TC9125BP can be turned on/off by the signal of mode setting data A5 keeping the reference frequency at 12.5 kHz.

Namely, when A5, B5, C5 = 1, 0, 1, the frequency division output signal appears on  $P_{OUT}-1$  and when A5, B5, C5 = 0, 0, 1, the frequency division output stops keeping  $P_{OUT}-1$  at "H" level.

- 2) When the frequency division output of programmable counter is connected to  $+50~\mathrm{kHz}$  terminal of prescaller, the local oscillator frequency is shifted by  $+50~\mathrm{kHz}$  and consequently the receiving frequency is also shifted by  $+50~\mathrm{kHz}$

- 2. Therefore, P<sub>OUT</sub>-1 terminal and +50 kHz terminal of prescaller is connected together. If the programe data is varied in such manner that A<sub>5</sub> = "0" with the frequency division data is N, then A<sub>5</sub> = "1" keeping the data N as it is, and A<sub>5</sub> = "0" at the same time as N is stepped up to N+1,... the receiving frequency can be scanned with 50 kHz step.

- 3. IF Fine Adjustment with 50 kHz Channel Step

- 1) IF fine adjustment of TC9125BP is further advanced providing two programmable counter frequency division output terminals (P<sub>OUT</sub>-1 and P<sub>OUT</sub>-2) enabling IF fine adjustment with 50 kHz channel step for European areas. Namely, always connecting P<sub>OUT</sub>-1 terminal to +50 kHz terminal, as previously explained, if P<sub>OUT</sub>-2 terminal is connected to +25 kHz or +50 kHz terminal, seven kinds of IF fine adjustments can be achieved.

- 2) In order to achieve fine adjustment of negative side, the controller is equipped with the function that the programmable counter frequency division data to TC9125BP in FM band can be arbitrarily decremented by -1.

T-50-17

3) Fig. 9 illustrates the connection of IF fine adjustment with 50 kHz channel step.

FIG. 9 CONNECTION FOR IF FINE ADJUSTMENT

4) The connections to perform seven kinds of IF fine adjustments in Fig. 9 are as shown in Table 6.

Table 6

| DESIRED I | F FREQUENCY | 50 kHz S | STEP FOR | EUROPEAN FM                        |

|-----------|-------------|----------|----------|------------------------------------|

| IF [MHz]  | ⊿ IF [kHz]  | A        | В        | FREQUENCY<br>DIVISION<br>FACTOR -1 |

| 10.775    | +75         | 0        | 0        |                                    |

| 10.750    | +50         |          | 0        |                                    |

| 10.725    | +25         | 0        |          |                                    |

| 10.700    | 0           | 1        |          | * 1                                |

| 10.675    | -25         | 0        | 0        | 0                                  |

| 10.650    | -50         |          | 0        | 0                                  |

| 10.625    | <b>-</b> 75 | 0        |          | 0                                  |

- (Notes) 1. 0 in the columns of (A) and (B) indicates that switches (A) and/or (B) should be turned on.

- 2. 0 in the column of frequency division factor -1 indicates that the frequency division data sent to TC9125BP is -1 shifted by the controller.

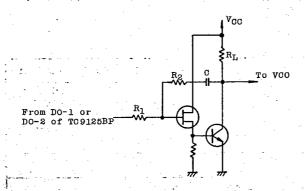

#### CONFIGURATION OF ACTIVE LOW PASS FILTER

The low pass filter of PLL is to convert the digital output from the phase comparator to analog output voltage, which controls VCO.

As an example here, active low pass filter with high input impedance obtained by Darlington connection of FET and NPN transistor is shown.

LOW PASS FILTER CIRCUIT FIG. 10

(Note): Although TC9125BP is equipped with two terminals of phase comparator outputs, it is not required to use both of them. TOSHIBA, ELECTRONIC D2 D

DE 9097247 0017866 7

### TC9125BP

T-50-17

=AUDIO DIGITAL IC

T-50-17

:TOSHIBA